Vorbereitung DT

Themen:

- Zahlensysteme: Horner-Schema, euklidischer Algorithmus

- Zahlendarstellungen: Wie wandle ich eine Zahl vom 10er-System ins Zahlensystem xy um und umgekehrt?

- Vorzeichen

- Betrags-Vorzeichen → Antwort

- Einerkomplement → Antwort

- Zweierkomplement → Antwort

- Exzess-q → Antwort

- Komma

- Festkomma → Beispiele

- Gleitkomma → Beispiele ($\pm \text{Mantisse} \cdot b^\text{Exponent}$)

- A practical approach to floats

- Wie wird NaN dargestellt? Wie wird $-\infty$ und $+\infty$ dargestellt?

- Was ist eine normalisierte Zahl, was eine denormalisierte?

Vorbereitung RO

Themen:

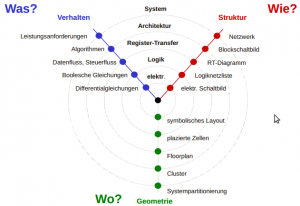

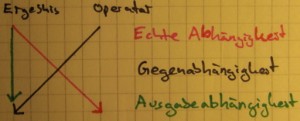

- Y-Diagramm

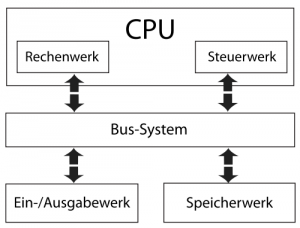

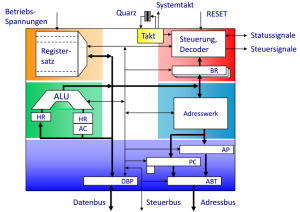

- Aufbau eines Mikroprozessors

- Umrechnen von Zahlensystemen

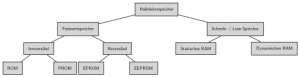

- RAM-Typen (DRAM, FPM-DRAM, EDO-RAM, SDRAM, DDRAM, DDR-SDRAM, RDRAM)

- Cache-Speicher

Begriffe

- Was sind Tristate-Treiber? → Antwort

- Was ist der Unterschied zwischen Assembler, Maschinensprache und Mikrobefehlen?

- Wofür stehen RISC und CISC und was sind Beispiele? → Antwort

- Was ist ein User/System-Bit, was ein Trace-Bit und was ein Decimal-Bit? → Antwort

- Welche Informationen können im Statusregister des Rechnewerkes stehen? → Antwort

- Welche Informationen können im Akkumulator stehen? → Antwort

- Warum benötigt die ALU Hilfsregister? → Antwort

- Entspricht das logische Rechtsschieben der Division durch zwei? → Antwort

- Was ist ein superskalarer Prozessor? → Antwort

- Was ist ein Little-Endian und was ist Big-Endian? → Antwort

- Was versteht man unter dem Nulladressformat? → Antwort

- Was ist eine „effektive Adresse“? → Antwort

- Was bedeutet ZF, CF, SF, OF und wozu sind sie jeweils gut?

- Was ist eine Load/Store-Architektur? → Antwort

- Was sind die fünf Schritte in der DLX-Pipeline-Verarbeitung? → Antwort

- In welcher Pipeline-Phase werden die Operanden aus dem memory geholt? → Antwort

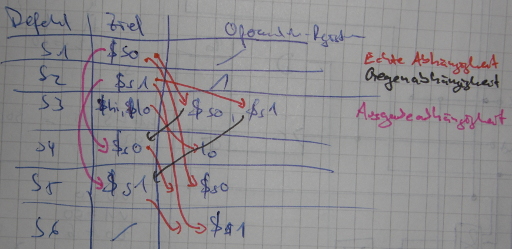

- Durch welche Abhängigkeiten entstehen Verzögerungen in der DLX-Pipeline und wann treten diese auf? → Antwort

- Was ist eine echte Datenabhängigkeit, was eine Gegenabhängigkeit und was eine Ausgabeabhängigkeit? → Antwort

- Was ist eine falsche Abhängigkeit? → Antwort

- Treten bei echten Abhängigkeiten immer Konflikte auf? → Antwort

- Welche Konflikte gibt es und wann können sie auftreten? → Antwort

- Welche Abhängigkeiten können bei der DLX-Pipeline zu Konflikten führen? → Antwort

- Wie kann man Datenkonflikte durch Software lösen? → Antwort

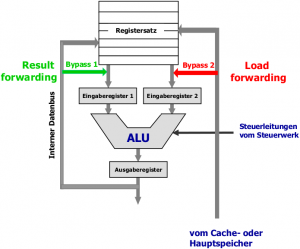

- Wie kann man Datenkonflikte durch Hardware lösen? → Antwort

- Nennen Sie ein Beispiel für einen Konflikt, der nicht durch Forwarding lösbar ist? → Antwort

- Wie kann man Ressourcenkonflikte lösen? → Antwort

- Was bedeutet tRAC, tRC, tCAC und tPC?

- Wie versteht man unter Bus-Schnüffeln? → Antwort

MIPS

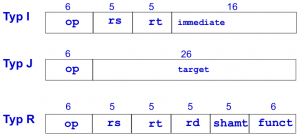

Befehlsformate

Quelle: Folien von Prof. Dr. Asfour

Typ-R-Befehle sind arithmetisch-logische Befehle wie add, sub, and, or sowie Vergleichsbefehle wie slt.

Typ-I-Befehle sind Lade- und Speicherbefehle sowie Verzweigungsbefehle:

lw $rt, imm($rs)

sw $rt, imm($rs)

beq $rs, $rt, immediate: Hier wird immediate als 16-Bit-vorzeichenbehaftete Zahl interpretiert und als Offset benutzt. Die Basisadresse ist dabei im PC. Also lautet die Zieladresse: (PC zum Zeitpunkt des Befehls + 4) + immediate

Grundlegende Befehle

| Syntax | Erklärung |

|---|---|

li $t0, 9 |

load immediate: Lädt eine Konstante in ein Register |

sll $rd, $rs, shamt |

shift left logical: $rd = $rs << shamt |

ble Rsrc1, Src2, label |

Branch on Less Than Equal: Rsrc1 ≤ Src2 |

bne $rs, $rt, imm |

Branch on not equal: if($rs!=$rt) PC = PC + imm (imm could also be a label) |

slti $rt, $rs, imm |

Store less than immediate: if($rs < imm) {$rt = 1;} else {$rt = 0} |

la Rdest, address |

Load computed address, not the contents of the location, into register Rdest |

MiMa

Quelle: Folien von Prof. Dr. Asfour

Fetch-Phase

In der Fetch-Phase muss die neue Instruktion ins IR geladen werden und der PC um eins erhöht werden:

- Takt: IAR → SAR; IAR → X; R = 1

- Takt: Eins → Y; ALU auf addieren; R = 1

- Takt: ALU auf addieren; R = 1

- Takt: Z → IAR

- Takt: SDR → IR

Das zugehörige Mikroprogramm ist:

0010 0001 0000 1000 1000 0000 0001

0001 0100 0000 0000 1000 0000 0010

0000 0000 0000 0001 1000 0000 0011

0000 1010 0000 0000 0000 0000 0100

0000 0000 1001 0000 0000 0000 0101

Fragen

Quelle: Folien von Prof. Dr. Asfour

Quelle: Folien von Prof. Dr. Asfour

- Holphase

- Dekodierphase

- Ausführungsphase

- Die Befehlsformate sind unterschiedlich lang

- Opcode-Prefetching

Quelle: Quelle: Folien von Prof. Dr. Asfour

| CISC | RISC |

|---|---|

| Komplexe Befehle, die in mehreren Taktzyklen ausgeführt werden | Einfache Befehle, die in einem Taktzyklus ausgeführt werden |

| Jeder Befehl kann auf den Speicher zugreifen | Nur Lade- und Speicherbefehle greifen auf den Speicher zu |

| Wenig Pipelining | Intensives Pipelining |

| Befehle werden von einem Mikroprogramm interpretiert | Befehle werden durch festverdrahtete Hardware ausgeführt |

| Befehlsformat variabler Länge | Befehlsformat fester Länge |

| Die Komplexität liegt im Mikroprogramm | Die Komplexität liegt im Compiler |

| Einfacher Registersatz | Mehrere Registersätze |

sw und lw aufpassen. Folgendes (sehr gekritzelte) Beispiel für die Klausur vom 26. Juli 2012:

Material

- TI-Website

- Meine Karteikarten (Siehe Anki auf Wikipedia und UbuntuUsers für mehr Informationen)

- titut.de, tutorium.chrismandery.de

StackOverflow:

Aufbau der Klausur

Die Klausuren sind alle sehr ähnlich aufgebaut. Eine typische Klausur hat 10 Aufgaben zu diesen Themen:

- Schaltfunktionen

- Spezielle Bausteine

- Laufzeiteffekte

- Schaltwerke

- Rechnerarithmetik und Codes

- Allgemeines: Ankreuzaufgaben

- MIPS-Assembler: C-Code in MIPS umwandeln und umgekehrt

- Pipelining: Datenkonflikte erkennen und mit NOPs beheben, eventuell gibts noch Forwarding

- Cache-Speicher

- Speicher

Termine und Klausurablauf

Datum: Mittwoch, den 3. April 2013 von 14:00 bis 16:00 Uhr

Ort: Gaede (bei mir; siehe Hörsaaleinteilung, die seit dem 2. April 2013 draußen ist)

Dauer: 1 h DT, 1 h RO

Punkte: (vermutlich) 90

Bestehensgrenze: (vermutlich) 40

Übungsschein: Wird nicht ins Studienportal eingetragen

Bonuspunkte:

- Übungsschein RO: 1 Bonuspunkt

- Übungsschein DT: 1 Bonuspunkt

- Für die Probeklausuren jeweils:

- Note „Sehr gut“: 2 Bonuspunkte

- Note „Gut“: 1,5 Bonuspunkte

- Note „Befriedigend“: 1 Bonuspunkt

- Note „Ausreichend“: 0,5 Bonuspunkte

Nicht vergessen

- Studentenausweis

- Kugelschreiber

Ergebnisse

Die Klausureinsicht ist am Montag, den 29. April 2013. Für die Einsicht muss man sich hier anmelden.